Most modern compute architectures improve arithmetic throughput or energy efficiency, but they remain fundamentally reset-driven. None formalize hardware-native continuity as a structural compute primitive.

| Architecture | Primary Strength | Structural Limitation |

|---|---|---|

| GPU / TPU | Massive parallel math throughput | Reset-driven execution — state reconstructed each cycle |

| Analog Accelerators | Energy-efficient matrix-vector multiplication | Continuous signals without persistent cross-epoch state evolution |

| Neuromorphic | Event-driven compute | State stored in memory arrays rather than substrate-native persistence |

| Reservoir Systems | Dynamic response | External readout and retraining required |

| Photonic MVM | Ultra-fast multiplication | Symbolic math embedded inside reset-driven pipelines |

All improve compute speed. None embed continuity directly into the hardware substrate.

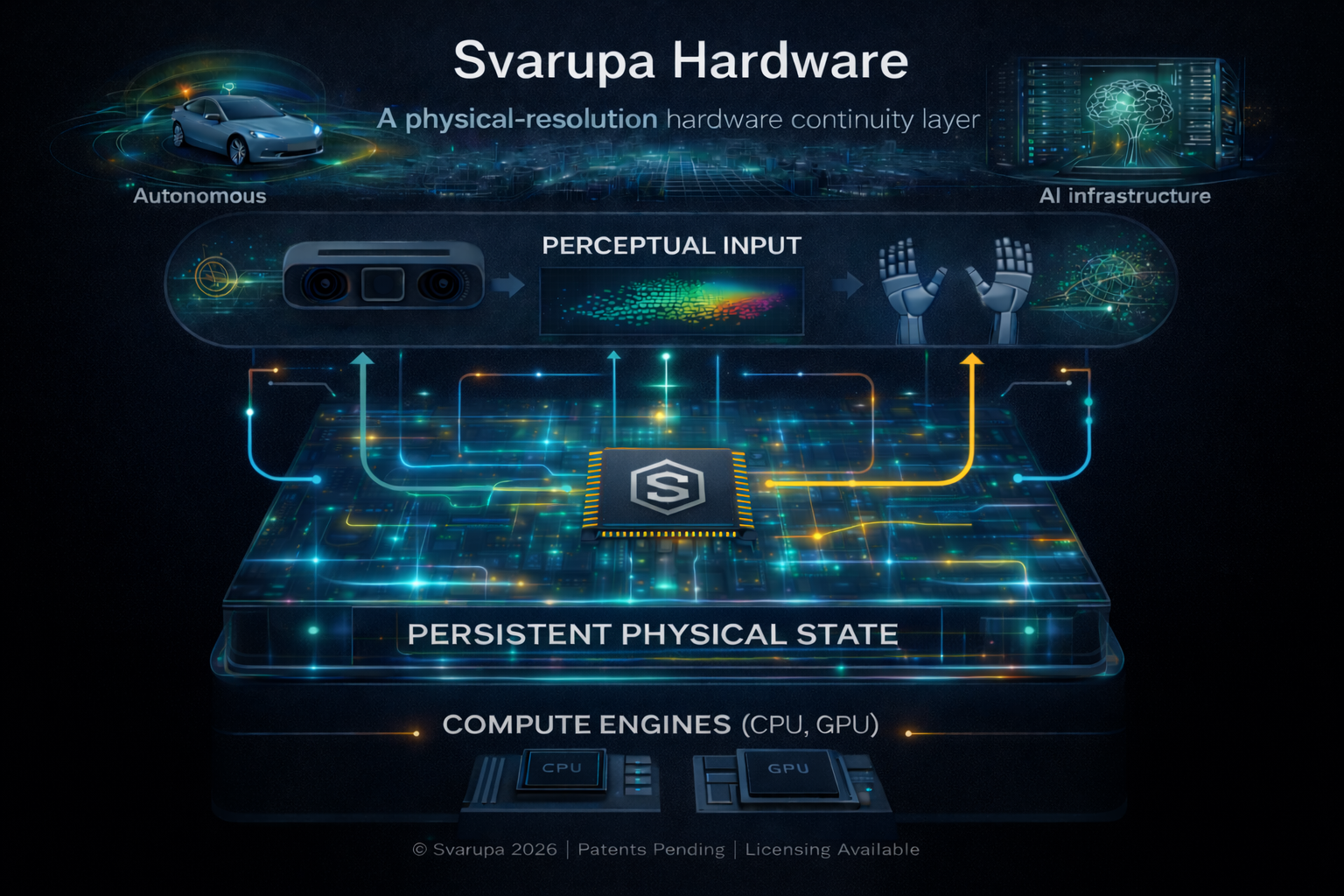

What is the “Practical Brain”?The Practical Brain is a hardware-native continuity architecture. Most modern AI hardware is reset-driven — requiring repeated reconstruction of internal state across execution cycles. Svarupa introduces persistence at the substrate level, allowing computation to stabilize across time rather than repeatedly reinitialize.

It represents an architectural shift from reconstructing state to carrying it forward.

How does Svarupa address state drift?In long-running autonomous systems, small reconstruction inconsistencies can accumulate, contributing to instability over time. Because Svarupa uses a persistent-state substrate, computation does not depend on repeated full reinitialization.

By reducing reconstruction cycles, the architecture aims to limit drift accumulation in continuous control environments.

Is Svarupa a symbolic processor?No. Traditional processors operate using discrete symbolic logic and gated digital transitions. Svarupa leverages nonlinear physical dynamics within a persistent substrate to enable convergence toward stable states.

While not symbolic in operation, its outputs are compatible with standard CMOS systems for higher-level control and decision logic.

What does “continuity as a compute primitive” mean?In conventional silicon architectures, state must be repeatedly reconstructed across clocked cycles. Svarupa treats persistence as a structural element of computation.

By embedding continuity into the hardware substrate itself, computation can evolve across time rather than restarting each cycle. This reduces energy and latency associated with repeated state reconstruction.

Svarupa’s focus is distinct: embedding hardware-native continuity directly into the substrate to enable persistent state evolution across time.

Is Svarupa compatible with current CMOS?

Is Svarupa compatible with current CMOS?

Yes. Svarupa integrates with existing CMOS systems but is not an accelerator. CMOS processors remain responsible for digital computation and control.

Svarupa provides persistent physical state continuity across time and exposes low-dimensional signals rather than accelerating arithmetic operations.

Integration uses standard silicon packaging and interfaces. No changes to existing fabs or digital toolchains are required.

How do I inquire about licensing or collaboration?Svarupa is currently validating its Stage 1 reference architecture. Development is focused on building a clean, internally developed IP foundation suitable for long-term hardware licensing.

Licensing inquiries and media requests can be directed to:

svarupa2000@gmail.com